## CC41C Introducción al Hardware Examen - Otoño 2011 Profesor: Luis Mateu

## Pregunta 1

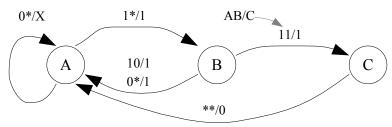

Utilice la metodología vista en clases para implementar el diagrama de estados de la figura. Haga la codificación de estados, tablas de verdad, mapas de *karnaugh* y obtenga las fórmulas algebraicas.

## Pregunta 2

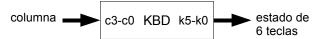

Ud. dispone del teclado de la figura, que está organizado como una matriz de 16 columnas de 6 teclas cada una. Para leer el estado de un columna completa (6 teclas) se suministra como entrada en **c3-c0** el número de la columna. El teclado entrega en **k5-k0** el estado de las 6 teclas pertenecientes a la columna. No es posible leer 2 columnas al mismo tiempo.

Parte a.- Construya una interfaz para este teclado considerando un microcontrolador con un bus de direcciones de 16 bits y bus de datos de 8 bits. Su interfaz debe poseer 16 puertos de entrada en las direcciones 0xFF00 a 0xFF0F (en hexadecimal). Cada uno de estos puertos sirve para leer una columna del teclado. No implemente KBD (es un dato del problema).

Parte b.- Programe la rutina:

que entrega verdadero si la tecla de coordenadas (fila,col) está presionada.

## Pregunta 3

(a) La figura muestra un extracto del contenido de un *cache* de 64 KB de 2 grados de asociativad y líneas de 16 bytes. El computador posee un bus de direcciones de 20 bits. El cache se organiza en 2 bancos, cada uno con 4096 líneas. Por ejemplo en la línea 4f2 (en hexadecimal) del banco izquierdo se almacena la línea de memoria que tiene como etiqueta 04f2 (es decir, la línea que va de la dirección 04f20 en hexadecimal a la dirección 04f2f).

| línea | Banco 1            |  | Banco 2            |  |

|-------|--------------------|--|--------------------|--|

| cache | etiqueta contenido |  | etiqueta contenido |  |

| 301   | 4301               |  | 2301               |  |

| 4f2   | 04f2               |  | a4f2               |  |

| c36   | dc36               |  | 1c36               |  |

Un programa accede a las siguientes direcciones de memoria: a4f28, dc360, 53014, 2301c, 1c360, ec368, 84f20, dc36c. Conteste (i) cuál es la porción de la dirección que se usa como *etiqueta*, (ii) cuál es la porción de la dirección que se usa para indexar *el cache*, y (iii) qué accesos a la memoria son aciertos en el cache y cuáles son desaciertos, mostrando un posible estado final del cache.

(b) Implemente el módulo Y-SEL de M32.